I. Detailed Explanation of Software and Tools in Front End Chip Design

Front-end design is the initial stage of digital chip development, with the core objective of deriving a gate-level netlist from functional specifications. This process mainly includes: specification definition, architecture design, HDL programming, simulation verification, logic synthesis, timing analysis, and formal verification.

✅ Specification Definition and Architecture Design

⬛ Main Task: Clarify the chip’s functions, performance, and module partitioning.

Common Tools:

VisualHDL (Summit): A language-level architecture modeling tool that supports building inter-module relationships graphically, helping developers clearly define the system architecture from a functional perspective.

Renoir (Mentor): Supports converting architecture into hardware description language; a visual architecture design tool, akin to a “Visio for hardware design.”

Composer (Cadence): Used for building schematics and block diagrams, suitable for early-stage system-level prototype design.

✅ HDL Coding (RTL Design)

⬛ Main Task: Use hardware description languages (Verilog or VHDL) to describe various functional modules.

Development Environment:

Text Editors (e.g., Vim, Emacs): Suitable for experienced engineers to write HDL code directly.

EDA Integrated Development Environments (e.g., Vivado, Quartus): Feature code highlighting, syntax checking, and project management capabilities.

⚠️ Note: Verilog is currently the industry’s mainstream language, comparable to using C language in software development to describe algorithm logic, while Verilog describes hardware behavior.

✅ Functional Simulation (Pre-Simulation)

⬛ Verifies whether RTL code logic meets specification requirements.

Main Simulation Tools:

ModelSim (Mentor): Beginner-friendly, widely used in education and early-stage verification.

VCS (Synopsys): Industrial-grade simulation platform supporting high-performance simulation and debugging.

NC-Verilog (Cadence): Integrated in the Cadence environment, facilitating collaboration with other tools.

Functional simulation is similar to “software unit testing,” using waveform and signal tracing tools to analyze whether the design behavior meets expectations.

✅ Logic Synthesis

⬛ Converts RTL code into a gate-level circuit netlist, preparing for back-end design.

Main Synthesis Tools:

Design Compiler (Synopsys): Industry standard, supports complex constraint management and optimization.

BuildGates (Cadence): Deeply integrated with the Cadence flow, suitable for small to medium projects.

Leonardo Spectrum (Mentor): Suitable for certain specific flows or academic projects.

Analogy: Logic synthesis is like compiling a high-level language into assembly code—except the target is a “gate library” rather than an instruction set.

✅ Static Timing Analysis (STA)

⬛ Verifies whether the circuit meets setup/hold time requirements under clock driving.

Common STA Tools:

PrimeTime (Synopsys): Industry mainstream with high precision and comprehensive functionality.

Tempus (Cadence): Integrates with physical design environments, suitable for complex chips.

SST Velocity (Mentor): Ideal for users of the Mentor toolchain.

STA does not require input stimulus vectors—it models all path delays to perform comprehensive timing analysis, which differs from functional simulation.

✅ Formal Verification

⬛ Checks whether the netlist after logic synthesis is functionally equivalent to the RTL, preventing functional deviation.

Common Tools:

Formality (Synopsys): High-precision equivalence checking tool, capable of handling large-scale netlists.

LEC (Cadence): Commonly used in verification after synthesis, optimization, and DFT.

FormalPro (Mentor): Suitable for formal verification tasks following Mentor synthesis tools.

⚠️ Functional equivalence verification is like comparing whether the original program and the compiled result implement the same logic.

II. Summary (Design Flow and Tool Comparison Table)

| Stage | Example Tools (by Vendor) |

|---|---|

| Architecture | VisualHDL (Summit), Renoir (Mentor), Composer (Cadence) |

| HDL Programming | Any text editor, Vivado, Quartus |

| Functional Sim | ModelSim (Mentor), VCS (Synopsys), NC-Verilog (Cadence) |

| Logic Synthesis | Design Compiler (Synopsys), BuildGates (Cadence), Leonardo (Mentor) |

| STA | PrimeTime (Synopsys), Tempus (Cadence), SST Velocity (Mentor) |

| Formal Verification | Formality (Synopsys), LEC (Cadence), FormalPro (Mentor) |

This design flow ensures a step-by-step convergence from functional specifications to gate-level implementation. Each tool plays a critical role. If front-end chip design is likened to constructing a skyscraper, then these tools correspond to blueprint drawing, structural calculations, functional rehearsals, material optimization, and design review—none of which can be omitted.

Related:

- Explore Logic Chips: Types and Key Differences with Analog

- What Is Chip Backend Design? Explained Simply

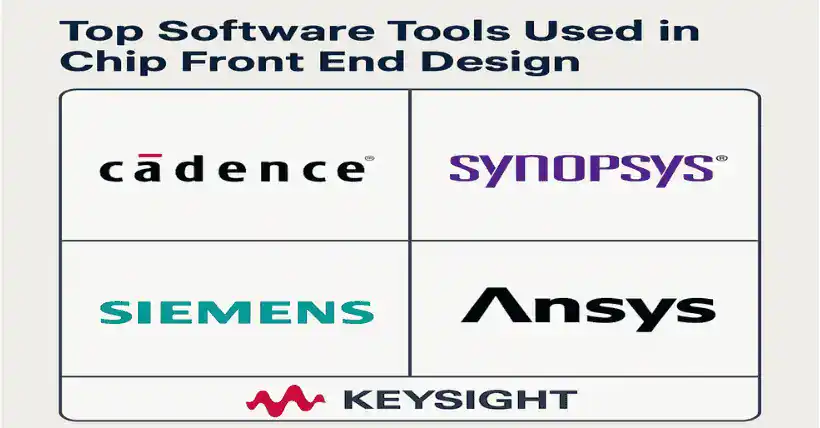

- Top EDA Tools Commonly Used in Chip Design Work

Disclaimer:

- This channel does not make any representations or warranties regarding the availability, accuracy, timeliness, effectiveness, or completeness of any information posted. It hereby disclaims any liability or consequences arising from the use of the information.

- This channel is non-commercial and non-profit. The re-posted content does not signify endorsement of its views or responsibility for its authenticity. It does not intend to constitute any other guidance. This channel is not liable for any inaccuracies or errors in the re-posted or published information, directly or indirectly.

- Some data, materials, text, images, etc., used in this channel are sourced from the internet, and all reposts are duly credited to their sources. If you discover any work that infringes on your intellectual property rights or personal legal interests, please contact us, and we will promptly modify or remove it.