Recently, an article from SemiEngineering pointed out that due to increasing complexity, chip manufacturing is shifting from monolithic chips to multi-chip modules. This trend requires more iterations and greater customization, making design and verification more time-consuming, and causing the first-pass success rate of tape-out to drop sharply.

According to data provided by Siemens, the first-pass success rate of tape-out in the semiconductor industry has hit a historic low. In addition, with the arrival of 2nm nodes, it’s increasingly difficult to improve chip yield under advanced process technologies.

The chip industry is facing serious challenges.

01

Chip Tape out Success Rate at a Historic Low

Tape-out for chip design is like taking a major exam.

Tape-out is a critical step to verify whether a chip design is successful—it involves sending the finalized design to a foundry to manufacture a prototype, and testing whether it meets design requirements or needs further optimization. If the prototype meets expectations, mass production can begin.

In the documentary Electronic Nation Memoirs, the feeling during tape-out is described this way: “For the two or three months after each chip tape-out, I was constantly anxious and sleepless. I kept thinking about what might be wrong… When the chip came back and I pressed RESET for the first time, I was incredibly nervous. The moment I released RESET was the moment that decided heaven or hell.”

According to Siemens data, the typical first-pass tape-out success rate for a chip is around 30%, but this fell to 24% in two years, and is projected to drop further to 14% in 2025—eight out of ten chips will fail.

Some failures are due to lax design processes, while others aren’t necessarily caused by functional issues. For example, if a chip runs 10% slower or consumes 10% more power than expected after tape-out, it may lose competitiveness in the market, requiring a redesign and new tape-out.

Many chip giants have stumbled on tape-out. For instance, AMD’s Bulldozer architecture and Qualcomm’s Snapdragon 810 both had setbacks.

AMD started developing the Bulldozer architecture in 2007, combining two physical cores into one module sharing an FPU and L2 cache. However, it failed to meet performance expectations. The complexity led to poor post-tape-out performance and wasted early R&D investment. Meanwhile, Intel’s Sandy Bridge processors performed better and gained market share.

Qualcomm’s Snapdragon 810, launched in 2015 as a flagship mobile processor, adopted advanced process nodes and high-performance designs. But post-tape-out, it suffered from serious heat and power issues, causing overheating and throttling in phones. Qualcomm had to revise the design, while Samsung gained ground with its more stable, low-power Exynos chips.

Four key reasons are behind the declining tape-out success rate:

- Growing Chip Complexity: Today’s chips increasingly use multi-chip modules, with components fabricated on different process nodes. For instance, advanced server chips might use 5nm for compute cores and 14nm for memory units, increasing coordination complexity between foundries and technologies.

- More Customized Chips: Custom chips are designed for specific data types, algorithms, or applications, requiring more elaborate design and verification. AI inference chips, for example, must be optimized for specific neural network structures, needing complete architectural and instruction set re-planning.

- Changed Development Models: Previously, chip development cycles lasted about 18 months. Now, companies need to launch more products faster. To meet tape-out schedules, many chipmakers compress design and verification timelines, even cutting corners in key steps. This raises the risk of undetected issues and failures.

- AI Pressure: AI’s rapid growth demands much higher chip performance, far beyond current semiconductor technology’s pace of advancement. Development and verification tools haven’t kept up, forcing engineers to use outdated tools under tight deadlines, increasing tape-out failure risks.

Brian Bailey, an editor at Semiconductor Engineering, noted: “AI’s soaring demand for compute power has far outpaced semiconductor architecture and tech advances. But development and verification tools haven’t caught up. Engineers are using old tools to do more in less time—no wonder tape-outs fail.”

The last major decline in tape-out success was in 2018.

Before 2018, the first-pass tape-out success rate for ASICs was stable around 30%, but it dropped to 26% that year. FPGA data is harder to track, but the rate of zero-defect projects can indicate trends. In 2018, only 16% of FPGA projects had zero escaped bugs—a decline even worse than that of ASICs.

This drop coincided with industry-wide migration from 28nm to 14nm and the early adoption of 7nm. Additionally, more chip designs began treating security as a core feature, especially in automotive and industrial sectors.

02

Chip Yield—A Major Roadblock

Even with a successful tape-out, production challenges remain—low yield is another major bottleneck hampering the chip industry’s growth.

Yield is a semiconductor fab’s core competitiveness and is often called its “lifeline.”

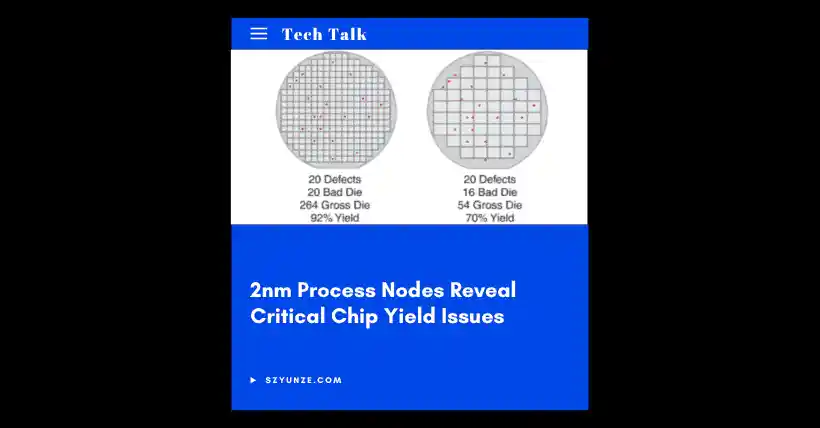

Chip yield refers to the ratio of functional chips to total chips produced. That is:

Yield = (Number of functional chips / Total chips produced) × 100%

For example, if 1,000 chips are made on a wafer and 950 are functional, the yield is:

(950 / 1000) × 100% = 95%

Yield must be measured and calculated at multiple stages, as defects can be introduced at any step. Typically, a yield of 70% or higher is required to proceed to mass production.

Even industry leaders like TSMC, Samsung, and Intel struggle with yield issues.

TSMC performs relatively well with advanced process yields. At the 2020 IEEE IEDM, TSMC disclosed an average 5nm test chip yield of 80%, with peak yields above 90%.

According to MSN, TSMC’s 3nm chip yields exceed 80%, attracting major clients like Apple and Qualcomm.

TSMC’s 2nm process outlook is also promising. Defect densities are reportedly similar to 3nm and 5nm, and it adopts the new GAAFET (Gate-All-Around FET) architecture. Compared to N3E (enhanced 3nm), 2nm offers 10–15% speed gains. TSMC’s 2nm yield has now exceeded 60%.

In contrast, Samsung’s yield struggles are more evident. Its 2nm process yield rose from 20–30% to over 40%, and the first Exynos 2600 chip using 2nm is scheduled for mass production in November 2025. Still, this lags behind TSMC’s 60%.

The 3nm situation is worse. SF3E-3GAE (1st-gen 3nm GAA) has yields of 50–60%, below the 70% target. SF3-3GAP (2nd-gen 3nm GAA) yields are around 20%, far below expectations, weakening Samsung’s foundry competitiveness. Even its own Exynos 2500 chip faces delays due to poor yield.

Intel is less transparent with yield data. Though a VP claimed Intel 4 process yields exceeded expectations, and Intel 3 met overall yield and performance goals, TF International analyst Ming-Chi Kuo said that early Panther Lake engineering samples using Intel 18A in early 2025 had yields below 20–30%.

Intel disputed this. VP of Investor Relations John Pitzer said at the Morgan Stanley TMT Conference: “Overall, we believe Intel 18A is comparable to TSMC N3 or N2. We’re proceeding on schedule and expect to complete tape-out for our first external customer in the first half of this year.”

Even the biggest players are grappling with low yield, showing how difficult the problem is.

Yield issues stem from multiple factors.

Materials: Silicon wafer quality, photoresist uniformity, dopant precision—all affect yield. Impurities or uneven photoresist can degrade chip performance. High-quality materials are expensive and technically demanding.

Environment & Equipment: Chips require ultra-clean environments—airborne particles can cause defects. Equipment stability, precision, and maintenance matter. New machines are costly and may have compatibility issues.

Process Technology: Lithography and etching steps are complex. Current methods have limited room for optimization. New technologies like EUV face high costs and technical barriers.

Quality Control: Without timely data collection and analysis during production, defects can’t be detected early or fixed, reducing yield.

03

Conclusion

The semiconductor industry must confront plummeting tape-out success rates and stagnant yield improvements.

To raise tape-out success, chipmakers should optimize design, use AI-assisted tools for accuracy, and strengthen design verification to catch problems early. Talent development is crucial to boost engineering capabilities. Close collaboration among design firms, foundries, and EDA vendors is also essential to integrate supply chain resources.

To improve yield, companies must refine process control and design optimization. Equipment upgrades and use of high-quality materials are necessary. Innovation is key—leveraging AI and big data for production monitoring, and exploring new materials and techniques. Establishing strict quality systems is critical, ensuring end-to-end oversight from raw materials to final products.

Solving these problems will require coordinated efforts in technology, talent, and across the entire industry chain.

Related:

Disclaimer:

- This channel does not make any representations or warranties regarding the availability, accuracy, timeliness, effectiveness, or completeness of any information posted. It hereby disclaims any liability or consequences arising from the use of the information.

- This channel is non-commercial and non-profit. The re-posted content does not signify endorsement of its views or responsibility for its authenticity. It does not intend to constitute any other guidance. This channel is not liable for any inaccuracies or errors in the re-posted or published information, directly or indirectly.

- Some data, materials, text, images, etc., used in this channel are sourced from the internet, and all reposts are duly credited to their sources. If you discover any work that infringes on your intellectual property rights or personal legal interests, please contact us, and we will promptly modify or remove it.