As Moore’s Law fails, the scale of high-performance computing chips continues to expand, and the enormous power consumption of data center clusters has become an unavoidable issue. As early as 2015, the SIA predicted that by 2040, the energy supply for global computing resources would no longer be sustainable. Now, with the explosion of artificial intelligence, the demand for computing resources has surged.

Taking the computing resources used to train AI large models as an example, the doubling speed every six months far exceeds the construction speed of high-performance computing clusters. There is no need to wait until 2040; by 2030, the resources required to train a single large model will exceed the total computing power of the TOP500 supercomputers, and the required power supply will reach a national level. Solving the problem of energy sustainability is unavoidable, but unless we slow down development or revolutionize computing methods, it is difficult to achieve this goal.

For AI, which has not yet entered a mature and fully profitable commercial model, slowing down development is naturally not an option. Therefore, the only option left is to revolutionize computing methods, and superconducting computing, which significantly reduces energy consumption, has naturally become the focus of many research directions.

1. Significantly reduce power consumption, with cooling as the biggest cost

In 2020, a research team from Yokohama National University in Japan demonstrated a superconducting CPU and successfully implemented tape-out. This processor mainly adopts the Josephson junction architecture, a classic three-layer superconducting device architecture, which is the basic component replacing transistors in superconducting logic units. Due to its unique physical properties, the switching power consumption of this device is only about 10^-21J, which greatly reduces dynamic power consumption compared to traditional CMOS devices. Additionally, the zero resistance characteristic of superconductors makes static power consumption approach zero.

The emergence of superconductors provides the greatest possibility for reducing power consumption, as they do not consume energy when current flows through them. The biggest energy expenditure is for the cooling solution required to operate at low temperatures, such as the superconducting chip processing unit, which often requires cooling to as low as 4K. Despite this, the near-zero resistance interconnects and digital logic constructed based on ultra-short pulses offer significant advantages for the large-scale expansion of modern computing resources.

Furthermore, as the scale of computing resources expands, the marginal cost of cooling solutions will decrease. According to imec research, once tens of petaflops are reached, superconducting computers will be more energy-efficient than traditional computers. The computing power requirements for this are already achievable by the top 30 supercomputers in the TOP500 list.

Recently, imec announced their superconducting computing units manufactured using standard CMOS technology. Processors built on this technology will be 100 times more efficient than the most efficient chips today, potentially fitting data center-level computing resources into a system the size of a shoebox.

2. Methods to bring superconductors out of the lab—compatible with existing CMOS manufacturing technology

Although superconductors can reduce power consumption and increase computing density, most research remains at the laboratory stage, making large-scale production almost a pipe dream. For example, the aforementioned Yokohama National University superconducting CPU is based on superconducting niobium, which performs well in predictable laboratory environments but presents many challenges in manufacturing processes.

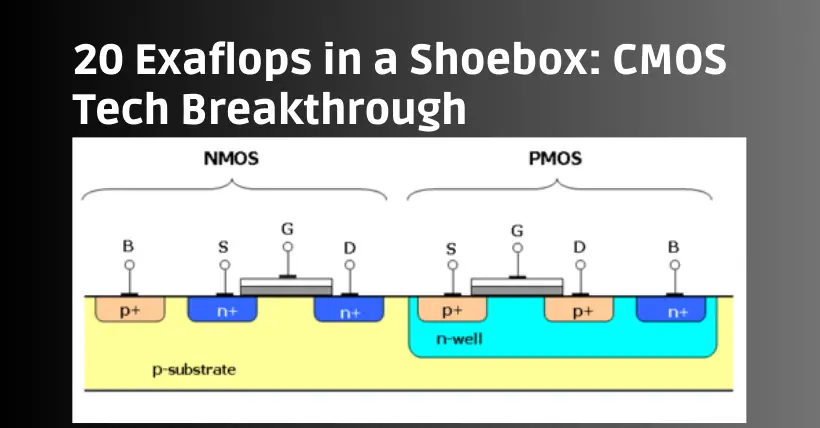

Niobium is very sensitive to the temperatures and surrounding materials used in traditional semiconductor processing and loses its superconducting capability when heated, making it incompatible with standard CMOS processes. To address this, imec switched to niobium-titanium nitride as the base superconducting material. Niobium-titanium nitride can withstand the temperatures used in CMOS manufacturing processes and reacts less with surrounding layers.

Imec also chose a new material for the barrier layer of the Josephson junction—amorphous silicon. Traditional Josephson junction barrier layer materials, such as aluminum oxide, can grow under controlled conditions, but to achieve densities much higher than CMOS process chips, further compression of their thickness is necessary. However, oxide films thin enough for this purpose are no longer manufacturable. Amorphous silicon allows for a thicker barrier layer, achieving a critical dimension of 210nm.

At the circuit level, it is also necessary to redesign the logic and memory structures. Imec developed a new logic architecture called pulse conservation logic, where the number of inputs and outputs remains the same, and the total number of single flux quanta (SFQs) is conserved. By combining different Josephson junctions and capacitors, SFQs are guided to different outputs to produce common logic operations like OR and AND. In Imec’s design, SRAM is also redesigned based on Josephson junctions, though DRAM still uses traditional silicon processes, but needs to be cooled from room temperature to 77K to improve efficiency.

3. Shoebox-sized data centers also need 3D stacking implementation

In CMOS-process-based digital chips, as shrinking transistors becomes increasingly difficult, we have begun to widely use 3D stacking technology to improve performance. However, due to the immense power and heat within the chip, stacking solutions face greater challenges, with cooling becoming the primary issue that most 3D stacking solutions must solve.

For superconducting chip designs, 3D stacking can also achieve higher density. Combining advanced packaging technologies such as silicon interposers and glass substrates, the superconducting processing units are stacked together with embedded superconducting SRAM and DRAM. Most of the chips will be immersed in liquid nitrogen and cooled to 4K.

In Imec’s simulations, they stacked 100 superconducting chipboards together, leaving only minimal space in between, resulting in a system with dimensions of 20x20x12 centimeters, similar to a shoebox. This shoebox-sized system has a total power consumption of only 500kW but can provide nearly 20 exaflops (BF16) of computing power.

This is just the first solution in Imec’s roadmap. Future products will further reduce the size of the Josephson junctions and interconnects. By further increasing the density of logic chips, the number of chipboards will decrease, thereby improving performance while reducing process complexity and cost.

4. Conclusion

Although superconducting computing provides a feasible technical route, even imec does not believe that superconducting data technology will replace traditional CMOS computing, but will only supplement specific applications. The main application scenarios for this technology are still in large data centers, providing cloud-based training and inference for AI and machine learning, as only such environments can support the cooling technology required for superconductors. In the consumer electronics field, traditional CMOS silicon processes are still irreplaceable.

It is worth mentioning that this technology can seamlessly integrate with imec’s superconducting qubit technology based on CMOS manufacturing processes, making it a perfect combination of electronic computing and quantum computing. However, even after solving the fundamental materials engineering design and architecture design, the circuit development design stage has yet to be completed, requiring EDA vendors to develop specific process tools for it.

Related:

Disclaimer: This article is created by the original author. The content of the article represents their personal opinions. Our reposting is for sharing and discussion purposes only and does not imply our endorsement or agreement. If you have any objections, please contact us through the provided channels.